# **Design of Analog Front-End for 128 Multi-Channel EEG Signal Acquisition in 90nm** es.1 **Technology**

# Gurajala Srinivas Praharshith, Sarvani Kunapareddy, Spurthi Nagulapally, Pavani.

hich pre-processes Abstract - This paper presents the design and implementation of a fully differential analog frontthe acquired Electro Encephalogram (EEG) signals before digitization. It consists of an analog multiplexer and a filter which can efficiently condition real-time EEG signals. The circuit has been designed so as to b mpatible with a 128 multi-channel data acquisition system and hence, a 128 multi-channel analog multiplexer has peen designed which aids in selecting the signal to be processed. Further, EEG signals are known to exist in the fr ency range of 0-5 KHz and amplitude range of 100ny to 10my. Hence, an eighth order low-pass filter with a bardwidth of 5 KHz, a stop band attenuation of -105dB, and a pass-band gain of 35.56dB has been implemented asing cascaded bi-quads. The entire filter possesses fully-differential architecture because of its ability to effective ower-line interference and on-chip SODI noise. Chebyshev implementation of Ackerberg-Mosseberg bi-quad hype in conserving the chip area and aided in effective noise suppression. The schematics of the above mentioned cir have been simulated in the 90nm technology.

# I. INTRODUCY OF

on potentials of the neurons, have, over the years provided The electrical signals generated due to the cumulative acquired through strategically placed electrodes either an insight into the functioning of the brain. The nal invasively or non-invasively, comprises of the ELG [4 7]. It is challenging to acquire invasive EEG signals and thus, noninvasively acquired EEG signals are nore popular [4-7]. But, these signals have to be thoroughly pre-processed through strict filtering before they can be sampled, digitized and stored on-chip.

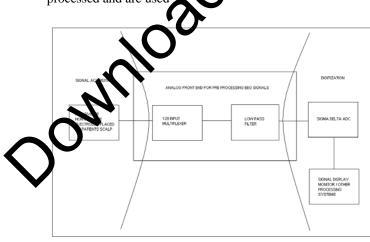

A block diagram of the pre-processi system and the components adjoining it, is shown in Fig.1. There are 128 electrodes placed spatially on the allow analysis of signals from different parts of brain. So, a 128 channel calp to input multiplexer is designed that the selection of any one of the 128 channels as the input to the filter. This filter's output is then fed a-delta ADC which gives out a 24-bit quantized signal. These signals can be processed and are used

Fig.1. Block Diagram of the System to diagnose several brain disorders and diseases.

As most of the neural activity occurs in the lower frequencies, it is aimed to design a low-pass filter with a cut off of 5 KHz [5]. The voltage range of the neural EEG signals is typically 100nV to 10mv [5]. The minimum voltage that needs to be resolved is 100nv, which when digitized needs 24 bits to be represented. Each bit in the resolution results in a -6dB/octave roll-off, hence we need a -140 dB/decade roll-off. Since the input voltages of the ADC are in the range of 600mV rail to rail, it is required to implement the filter with a gain of 35.56dB or 60V/V. The number of electrodes to be used is 128. Hence, it conditions to have a 128 multi-channel multiplexer.

The filter design is done in a bottom-up process. Initially, single stage operational amplifier (Op-Amp) and two stage Op-Amp are designed using telescopic Op-Amp with gain boosted first stage and a common source second stage. Ackerberg-Mossberg bi-quad uses ideal Op-Amp's cascaded in inverting and non-inverting comparations with a feedback using appropriate resistors and capacitors, providing required gain. In order to approximate the behaviour of designed Op-Amp's to the behaviour of ideal Op-Amp's, a tolerance of 1% in the transfer function is allowed. MATLAB simulations have been done and a gain of 40dB for single stage Op-Amp'undug gain of 60dB for two stage Op-Amp are fixed as ideal Op-Amp's. A cascade of four Ackerberg-Mossberg biquats is used to get the desired low-pass filter.

A decoder and a chain of transmission gates are used to design the analog multipleyer which facilitates the user to select the channel on which pre-processing has to be done.

# II. DESIGN FLOW

#### 2.1 Current Source Design

Current sources which supply current in the orders of milli-amperes condume huge on-die area. By using transistors working in saturation region and adjusting their sizes, any rate of the supply current can be mirrored and steered from a single current source to the entire circuit. Using this concept, a current source of micro-amperes is employed through which hundreds of micro-amperes of required current is mirrored into each of the Op-Amps in the circuit. We are using a  $100\mu$ A current source in our design.

#### 2.2. Amplifier Design

Before starting the design of the amplifie, servin specifications are available at our disposal. These include  $V_{DD}$ , Tail current  $I_{SS}$ , Maximum Slew rate, Unity Gan Bandwidth (UGBW), Load Capacitance  $C_L$ , Maximum power to be drawn and output swing. For the set of transistors to work as an amplifier, each of them has to work in the saturation region. Hence the condition needed to be satisfied, in case of a

MOS is:  $V_{ds} > V_{dsat}$  and PMOS is:  $V_{sd} > |V_{dsat}|$  (1)

Initially, we assume certain  $V_{ds}$  for each of the transistors. Further, we allocate a margin of twice the sum of the  $V_{dsat}$  of all the transistors and also allocate the amount of output swing. This margin voltage will be helpful in cases when there is a shifting of common-mode of the amplifier due to certain design approximations [2]. Hence, we cannot a formulate:

| $V_{dsatin} + V_{dsatload} = V_{DSAT}$ | (2) |

|----------------------------------------|-----|

| Margin = $2 V_{DSAT}$                  | (3) |

#### $V_{DSAT}$ +Margin + Output Swing = $V_{DD}$ (4)

To make sure that all the transistors in the branch are in saturation, we allocate a certain  $V_{ds}$ , just like how we allocated  $V_{dsat}$  in the previous step, to each of the transistors. The condition to be satisfied here is,

$$V_{dsin} + V_{dsload} = V_{DD} \tag{5}$$

In analog design, the finger width of each of the transistor is kept constant. This is to reduce gate resistance. Further, if we use a single finger instead of serially connected fingers, then the time for the current to travel from one end of

the finger to the other end is more. It is possible to calculate the trans-conductance of the input transistors, if the load capacitance and the UGBW are known. The relationship is as follows:

$$UGBW = g_{min} / (2 * \pi * C_L)$$

(6)

Further, with the given maximum power,  $P_{max}$ , it is possible to calculate the maximum amount of current that we can draw into the amplifier as,

$$P_{max} = V_{DD} * I_{SSmax} \tag{7}$$

For design purposes, it is possible to choose a convenient  $I_{SS}$  which is less than  $I_{SSmax}$ . Choosing a value too low will prompt us to use larger MOSFET's for the design, while choosing a value too large, say  $I_{SSmax}$ , we will be burning a large amount of power. Hence there exists a trade-off between area and power and it the decision of the designer which paves the way for further design. With the help of the calculated  $g_m$ , allocated  $V_{dsat}$ , allocated L and the current to be burnt we can calculate the W/L of the input transistors. It is to be made sure that the length, L of these transistors is kept to minimum. This is because, the entire switching activity happens at the transistor and for the circuit to be fast, we need the L to be minimum, which for a 90nm technology is given as 10 nm. The L for the load transistors is usually higher, in-order to obtain higher  $R_{out}$ , which ultimately will reflect on the pain of the amplifier.

It is needed for us to have a gain as high as 60dB and hence a telescopic single-stag applifier, gain boosted using auxiliary NMOS and PMOS amplifiers has been designed. Implementing this in Cadence, a gain of 64.5dB has been obtained.

#### 2.3 Common-Mode Feedback Design (CMFB)

Different topologies of CMFB are available for usage, and basing on the requirements of the user, the designer can choose [2]. The sizing strategy that is to be followed is as follow. The sizes of the four input transistors are equal, and are given by:

$(W/L)_{in} = 1/mirroring ratio *(W/L)_1$  (8)

Where  $(W/L)_1$  is the size of the input transistors of the amplifier. While, the sizes of the load transistors are given by,

$(W/L)_{load} = 1/mirroring ratio*2* (W/L)_4$

Where  $(W/L)_4$  is the size of the load transister in the amplifier.

#### 2.4 Differential Amplifier Second-Stage Design

The second-stage is usually a compone source amplifier. Also, if the first-stage is a PMOS based amplifier, then the second-stage is an NMOS based amplifier. Now, the second-stage of the Op-Amp introduces a new set of poles, in addition to the poles introduced by the first stage [3]. So, in-order for the system to be stable and to ensure that these poles do not interfere, we but the poles of the second-stage further away from those of the first-stage by at least5 times. This can be achieved by burning 5 times of the current being burnt in the first stage. The sizes can then be calculated from the delign steps as mentioned in the first stage. To obtain high swing of 600mV rail to rail, two stage amplifier has been designed which gives a gain of 82.34 dB.

#### 2.5. Frequency Compensation

The proce margin to be achieved is 60 degrees, to ensure that the system is stable. Frequency compensation involves placing a resistance-capacitance pair in between the two stages of the Op-Amp. The values of the resistance and apacitance are varied using the parametric analysis of the Cadence tool and the phase margin is plotted. The values if resistance and capacitance for which the phase margin is 60 degrees, is taken as the compensation resistance-capacitance.

#### 2.6 Bi-quad Design

The Ackerberg-Mossberg bi-quad is found to operate at relatively high frequencies even for large Q values [1]. Therefore we used an Ackerberg-Mossberg bi-quad in our design. The number of poles required toachieve the given

cut-off and roll-off is found to be eight. The transfer function of the filter is calculated using the cut-off frequency and the location of the poles. The transfer function is divided into four second-order transfer functions and each of the transfer functions is implemented using a different bi-quad. The capacitance and resistance values for each of the bi-quads are calculated separately according to the placement of the poles using the equation.

#### $\omega_0 = 1/R * C$

(10)

#### where, $\omega_0$ is the frequency of the pole location [1].

In order to minimize the area of the system, small capacitances (in the order of pico farads) are used. A gain of 35.56 dB has to be achieved. This is done by distributing the gain among the four bi-quads according to the value of Q. The first three bi-quads require only single stage Op-Amps and hence the single stage Op-Amp which we have designed earlier can be used. Since the output swing is also a major concern in our design, the last bi-quad requires a single stage Op-Amps and a two stage Op-Amps. All the bi-quads are connected in series and the output of the last bi-quad is taken as the final output of the filter.

#### 2.7 128 Input Multiplexer

Initially the signal which is to be pre-processed i.e., filtered and amplified has to be selected. The selection is done by choosing one channel among the 128 channels available and the signal obtained brough that channel is preprocessed. The signal inputs are directly given to a chain of transmission gates. These transmission gates are controlled by using a decoder. This whole system acts as a 128 multi-channel multiplexer which has the decoder inputs as the select lines. Thus the required channel on which the pre-processing has to be done is selected by manually controlling the decoder inputs. It is also possible to design a signal logic, based on the requirements of the user which can then perform automatic selection of the input.

## III. SIMULATION RESULTS

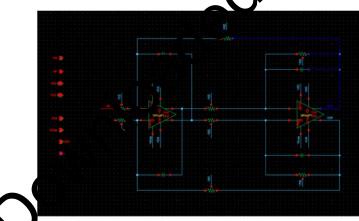

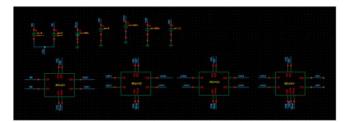

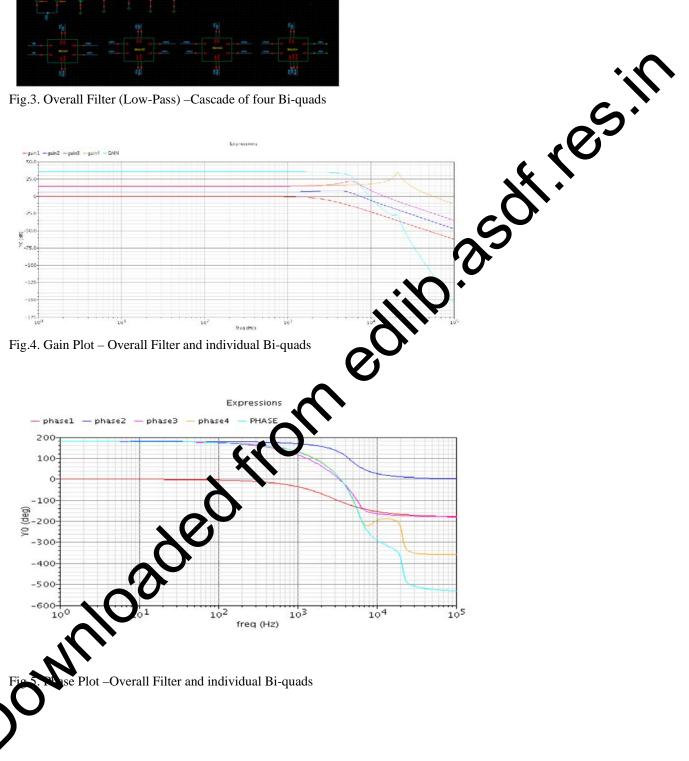

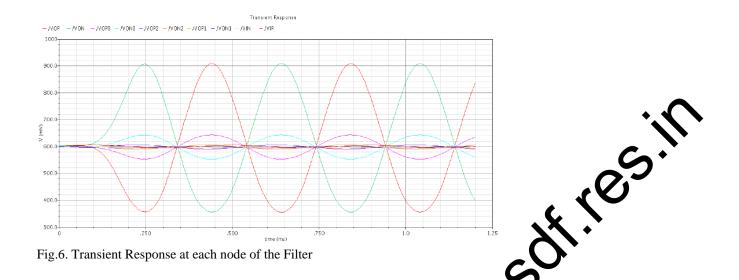

The simulation results of our system are shown here. Fig.2 is the Cadence implementation of the differential Ackerberg-Mossberg bi-quad with two Op-Amp connected in inverting and non-inverting configurations. Fig.3 is the overall filter design as a cascade of four 41-quad. Fig.4 and 5 are the gain and phase plots of the overall filter and of each bi-quad respectively. Fig.6 is the transient response at each node of the filter when a 5mV rail to rail sinusoid of frequency 2.5 KHz is given as input.

ig.2. Bi-quad Design

289

Fig.3. Overall Filter (Low-Pass) - Cascade of four Bi-quads

#### CONCLUSION

The eighth order low-pass filter which we have designed has a cut of which is approximately equal to 5 KHz and a roll off of -140.56dB at 50 KHz. The Chebyshev in tion of Ackerberg-Mosseberg bi-quad provided better results when compared to Tow-Thomas Butterwor ementation and Sallen key bi-quad. The μì output common-mode of the designed operational amplifier is and the output swings obtained were from 300mV to 900mV which gives a rail to rail of 600mV as a quired. Unity Gain bandwidth of this Op-Amp is 700MHz. The overall filter has a gain of 35.56dB be bailed cascading four bi-quads each with a gain of 20.383mdB, 5.976dB, 13.995dB and 15.572dB respe he swings of the bi-quads are 7mV, 18mv, 91mV and 583mV respectively for 2.5 KHz input frequence occupied by the system is approximately 0.4mm<sup>2</sup> and the power consumed is nearly 30mW.

### REFERENCES

[1] Schaumann, Rolf, and Mac I. Yay Valkenburg. Design of analog filters. Oxford University Press, 2009.

[2] Razavi, Behzad. Design of malog CMOS integrated circuits. Tata McGraw-Hill Education, 2002.

[3] Gray, Paul R., and Robert G. Meyer. Analysis and design of analog integrated circuits. John Wiley and Sons,

#### Inc., 1990.

[4] Farshchi, Shiha, Javan Mody, and Jack W. Judy. "A TinyOS-based wireless neural interface." Engineering in Medicine and Diology Society, 2004. IEMBS'04. 26<sup>th</sup> Annual International Conference of the IEEE. Vol. 2.IEEE, 2004.

[5] Share ui, Farzaneh, et al. "The 128-channel fully differential digital integrated neural recording and stimulation in Sacce Biomedical Circuits and Systems, IEEE Transactions on 4.3 (2010): 149-161.

G sselin, Benoit. "Recent advances in neural recording microsystems." Sensors 11.5 (2011): 4572-4597. Hirata, Masayuki, et al. "A fully-implantable wireless system for human brain-machine interfaces using brain urface electrodes: W-HERBS." IEICE transactions on communications 94.9 (2011): 2448-2453.